# Athens Journal of Technology & Engineering

Quarterly Academic Periodical, Volume 11, Issue 2, September 2024

URL: <a href="https://www.athensjournals.gr/ajte">https://www.athensjournals.gr/ajte</a>

Email: <a href="mailto:journals@atiner.gr">journals@atiner.gr</a>

e-ISSN: 2241-8237 DOI: 10.30958/ajte

## **Front Pages**

TEODORO GEORGIADIS, LETIZIA CREMONINI, DANIELA FAMULARI, MARIANNA NARDINO, FEDERICA ROSSI, CRISTINA SILIGARDI, ERIKA IVETH CEDILLO-GONZÁLEZ, SIMONE BANDINI & MATTEO NASCI

<u>A Methodological Proposal for the Characterization of Building Heritage</u> from the Second Twentieth Century for Renovation Purposes

FLORIAN DEEG, XIANGYUAN WU & SEBASTIAN M. SATTLER

Self-locking Domino Logic Pipelined Controller for RISC-V in FPGA

TILL HÄNISCH, LEA SCHMITT & FRANZISKA SCHÜTZ

<u>Transforming CS Curricula into EU-standardized Micro-Credentials</u>

<u>- The Hard Parts</u>

## JUNPENG FAN

A Visual Cross-software Evaluation Platform for Perseveration and Revitalization of Historical Villages: Application in Qinchuan Historical Village, Zhejiang Province

## Athens Journal of Technology & Engineering

*Published by the Athens Institute for Education and Research (ATINER)*

#### **Editors**

- Dr. Timothy M. Young, Director, <u>Center for Data Science (CDS)</u> & Professor and Graduate Director, The University of Tennessee, USA.

- Dr. Panagiotis Petratos, Vice-President of Information Communications Technology, ATINER & Fellow, Institution of Engineering and Technology & Professor, Department of Computer Information Systems, California State University, Stanislaus, USA.

- Dr. Nikos Mourtos, Head, <u>Mechanical Engineering Unit</u>, ATINER & Professor, San Jose State University USA.

- Dr. Theodore Trafalis, Director, <u>Engineering & Architecture Division</u>, ATINER, Professor of Industrial & Systems Engineering and Director, Optimization & Intelligent Systems Laboratory, The University of Oklahoma, USA.

- Dr. Virginia Sisiopiku, Head, <u>Transportation Engineering Unit</u>, ATINER & Associate Professor, The University of Alabama at Birmingham, USA.

#### Editorial & Reviewers' Board

https://www.athensjournals.gr/ajte/eb

#### Administration of the Journal

- 1. Vice President of Publications: Dr Zoe Boutsioli

- 2. General Managing Editor of all ATINER's Publications: Ms. Afrodete Papanikou

- 3. ICT Managing Editor of all ATINER's Publications: Mr. Kostas Spyropoulos

- 4. Managing Editor of this Journal: Ms. Effie Stamoulara

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

\*

ATINER is an Athens-based World Association of Academics and Researchers based in Athens. ATINER is an independent and non-profit Association with a Mission to become a forum where Academics and Researchers from all over the world can meet in Athens, exchange ideas on their research and discuss future developments in their disciplines, as well as engage with professionals from other fields. Athens was chosen because of its long history of academic gatherings, which go back thousands of years to Plato's Academy and Aristotle's Lyceum. Both these historic places are within walking distance from ATINER's downtown offices. Since antiquity, Athens was an open city. In the words of Pericles, Athens"...is open to the world, we never expel a foreigner from learning or seeing". ("Pericles' Funeral Oration", in Thucydides, The History of the Peloponnesian War). It is ATINER's mission to revive the glory of Ancient Athens by inviting the World Academic Community to the city, to learn from each other in an environment of freedom and respect for other people's opinions and beliefs. After all, the free expression of one's opinion formed the basis for the development of democracy, and Athens was its cradle. As it turned out, the Golden Age of Athens was in fact, the Golden Age of the Western Civilization. Education and (Re)searching for the 'truth' are the pillars of any free (democratic) society. This is the reason why Education and Research are the two core words in ATINER's name.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

The Athens Journal of Technology & Engineering (AJTE) is an Open Access quarterly double-blind peer reviewed journal and considers papers from all areas engineering (civil, electrical, mechanical, industrial, computer, transportation etc), technology, innovation, new methods of production and management, and industrial organization. Many of the papers published in this journal have been presented at the various conferences sponsored by the <a href="Engineering & Architecture Division">Engineering & Architecture Division</a> of the Athens Institute for Education and Research (ATINER). All papers are subject to ATINER's <a href="Publication Ethical Policy and Statement">Publication Ethical Policy and Statement</a>.

# The Athens Journal of Technology & Engineering ISSN NUMBER: 2241-8237- DOI: 10.30958/ajte Volume 11, Issue 3, September 2024 Download the entire issue (PDF)

| Front Pages                                                                                                       | i-vii |

|-------------------------------------------------------------------------------------------------------------------|-------|

| A Methodological Proposal for the Characterization of<br>Building Heritage from the Second Twentieth Century for  | 187   |

| Renovation Purposes                                                                                               |       |

| Teodoro Georgiadis, Letizia Cremonini, Daniela Famulari,<br>Marianna Nardino, Federica Rossi, Cristina Siligardi, |       |

| Erika Iveth Cedillo-González, Simone Bandini &                                                                    |       |

| Matteo Nasci                                                                                                      |       |

| Self-locking Domino Logic Pipelined Controller for RISC-V in FPGA                                                 | 201   |

| Florian Deeg, Xiangyuan Wu & Sebastian M. Sattler                                                                 |       |

| <u>Transforming CS Curricula into EU-standardized</u><br>Micro-Credentials – The Hard Parts                       | 219   |

| Till Hänisch, Lea Schmitt & Franziska Schütz                                                                      |       |

| A Visual Cross-software Evaluation Platform for                                                                   | 235   |

| Perseveration and Revitalization of Historical Villages:                                                          |       |

| Application in Qinchuan Historical Village, Zhejiang                                                              |       |

| <u>Province</u>                                                                                                   |       |

| Junpeng Fan                                                                                                       |       |

# Athens Journal of Technology & Engineering Editorial and Reviewers' Board

#### **Editors**

- Dr. Timothy M. Young, Director, <u>Center for Data Science (CDS)</u> & Professor and Graduate Director, The University of Tennessee, USA.

- **Dr. Panagiotis Petratos,** Vice-President of Information Communications Technology, ATINER & Fellow, Institution of Engineering and Technology & Professor, Department of Computer Information Systems, California State University, Stanislaus, USA.

- Dr. Nikos Mourtos, Head, <u>Mechanical Engineering Unit</u>, ATINER & Professor, San Jose State University USA.

- **Dr. Theodore Trafalis**, Director, <u>Engineering & Architecture Division</u>, ATINER, Professor of Industrial & Systems Engineering and Director, Optimization & Intelligent Systems Laboratory, The University of Oklahoma, USA.

- **Dr. Virginia Sisiopiku**, Head, <u>Transportation Engineering Unit</u>, ATINER & Associate Professor, The University of Alabama at Birmingham, USA.

#### **Editorial Board**

- Dr. Marek Osinski, Academic Member, ATINER & Gardner-Zemke Professor, University of New Mexico, USA

- Dr. Jose A. Ventura, Academic Member, ATINER & Professor, The Pennsylvania State University, USA.

- Dr. Nicolas Abatzoglou, Professor and Head, Department of Chemical & Biotechnological Engineering, University of Sherbrooke, Canada.

- Dr. Jamal Khatib, Professor, Faculty of Science and Engineering, University of Wolverhampton, UK.

- Dr. Luis Norberto Lopez de Lacalle, Professor, University of the Basque Country, Spain.

- Dr. Zagabathuni Venkata Panchakshari Murthy, Professor & Head, Department of Chemical Engineering, Sardar Vallabhbha National Institute of Technology, India.

- Dr. Yiannis Papadopoulos, Professor, Leader of Dependable Systems Research Group, University of Hull, UK.

- Dr. Bulent Yesilata, Professor & Dean, Engineering Faculty, Harran University, Turkey.

- Dr. Javed Iqbal Qazi, Professor, University of the Punjab, Pakistan.

- Dr. Ahmed Senouci, Associate Professor, College of Technology, University of Houston, USA.

- Dr. Najla Fourati, Associate Professor, National Conservatory of Arts and Crafts (Cnam)-Paris, France.

- Dr. Ameersing Luximon, Associate Professor, Institute of Textiles and Clothing, Polytechnic University, Hong Kong.

- Dr. Georges Nassar, Associate Professor, University of Lille Nord de France, France.

- Dr. Roberto Gomez, Associate Professor, Institute of Engineering, National Autonomous University of Mexico, Mexico

- Dr. Aly Mousaad Aly, Academic Member, ATINER & Assistant Professor, Department of Civil and Environmental Engineering, Louisiana State University, USA.

- Dr. Hugo Rodrigues, Senior Lecturer, Civil Engineering Department, School of Technology and Management, Polytechnic Institute of Leiria, Portugal.

- Dr. Saravanamuthttu Subramaniam Sivakumar, Head & Senior Lecturer, Department of Civil Engineering, Faculty of Engineering, University of Jaffna, Sri Lanka.

- Dr. Hamid Reza Tabatabaiefar, Lecturer, Faculty of Science and Technology, Federation University, Australia.

- Vice President of Publications: Dr Zoe Boutsioli

- General Managing Editor of all ATINER's Publications: Ms. Afrodete Papanikou

- ICT Managing Editor of all ATINER's Publications: Mr. Kostas Spyropoulos

- Managing Editor of this Journal: Ms. Eirini Lentzou (bio)

## President's Message

All ATINER's publications including its e-journals are open access without any costs (submission, processing, publishing, open access paid by authors, open access paid by readers etc.) and is independent of presentations at any of the many small events (conferences, symposiums, forums, colloquiums, courses, roundtable discussions) organized by ATINER throughout the year and entail significant costs of participating. The intellectual property rights of the submitting papers remain with the author. Before you submit, please make sure your paper meets the basic academic standards, which includes proper English. Some articles will be selected from the numerous papers that have been presented at the various annual international academic conferences organized by the different divisions and units of the Athens Institute for Education and Research. The plethora of papers presented every year will enable the editorial board of each journal to select the best, and in so doing produce a top-quality academic journal. In addition to papers presented, ATINER will encourage the independent submission of papers to be evaluated for publication.

The current issue is the third of the eleventh volume of the *Athens Journal of Technology & Engineering (AJTE)*, published by the <a href="Engineering & Architecture Division">Engineering & Architecture Division</a> of ATINER.

Gregory T. Papanikos, President, ATINER.

## Athens Institute for Education and Research

A World Association of Academics and Researchers

# 15<sup>th</sup> Annual International Conference on Civil Engineering 23-26 June 2025, Athens, Greece

The <u>Civil Engineering Unit</u> of ATINER is organizing its 15th Annual International Conference on Civil Engineering, 23-26 June 2025, Athens, Greece sponsored by the <u>Athens Journal of Technology & Engineering</u>. The aim of the conference is to bring together academics and researchers of all areas of Civil Engineering other related areas. You may participate as stream leader, presenter of one paper, chair of a session or observer. Please submit a proposal using the form available (https://www.atiner.gr/2025/FORM-CIV.doc).

#### **Academic Members Responsible for the Conference**

• **Dr. Dimitrios Goulias**, Head, <u>Civil Engineering Unit</u>, ATINER and Associate Professor & Director of Undergraduate Studies Civil & Environmental Engineering Department, University of Maryland, USA.

#### **Important Dates**

- Abstract Submission: 19 November 2024

- Acceptance of Abstract: 4 Weeks after Submission

- Submission of Paper: 26 May 2025

#### Social and Educational Program

The Social Program Emphasizes the Educational Aspect of the Academic Meetings of Atiner.

- Greek Night Entertainment (This is the official dinner of the conference)

- Athens Sightseeing: Old and New-An Educational Urban Walk

- Social Dinner

- Mycenae Visit

- Exploration of the Aegean Islands

- Delphi Visit

- Ancient Corinth and Cape Sounion

#### Conference Fees

Conference fees vary from 400€ to 2000€ Details can be found at: https://www.atiner.gr/fees

## Athens Institute for Education and Research

## A World Association of Academics and Researchers

# 13th Annual International Conference on Industrial, Systems and Design Engineering, 23-26 June 2025, Athens, Greece

The <u>Industrial Engineering Unit</u> of ATINER will hold its 13th Annual International Conference on Industrial, Systems and Design Engineering, 23-26 June 2025, Athens, Greece sponsored by the <u>Athens Journal of Technology & Engineering</u>. The aim of the conference is to bring together academics, researchers and professionals in areas of Industrial, Systems, Design Engineering and related subjects. You may participate as stream leader, presenter of one paper, chair of a session or observer. Please submit a proposal using the form available (https://www.atiner.gr/2025/FORM-IND.doc).

#### **Important Dates**

- Abstract Submission: 19 November 2024

- Acceptance of Abstract: 4 Weeks after Submission

- Submission of Paper: 26 May 2024

#### Academic Member Responsible for the Conference

• **Dr. Theodore Trafalis**, Director, <u>Engineering & Architecture Division</u>, ATINER, Professor of Industrial & Systems Engineering and Director, Optimization & Intelligent Systems Laboratory, The University of Oklahoma, USA.

#### **Social and Educational Program**

The Social Program Emphasizes the Educational Aspect of the Academic Meetings of Atiner.

- Greek Night Entertainment (This is the official dinner of the conference)

- Athens Sightseeing: Old and New-An Educational Urban Walk

- Social Dinner

- Mycenae Visit

- Exploration of the Aegean Islands

- Delphi Visit

- Ancient Corinth and Cape Sounion

More information can be found here: <a href="https://www.atiner.gr/social-program">https://www.atiner.gr/social-program</a>

#### **Conference Fees**

Conference fees vary from 400€ to 2000€ Details can be found at: <a href="https://www.atiner.gr/fees">https://www.atiner.gr/fees</a>

## A Methodological Proposal for the Characterization of Building Heritage from the Second Twentieth Century for Renovation Purposes

By Teodoro Georgiadis\*, Letizia Cremonini<sup>±</sup>, Daniela Famulari<sup>°</sup>, Marianna Nardino\*, Federica Rossi\*, Cristina Siligardi\*, Erika Iveth Cedillo-González.\*, Simone Bandini\* & Matteo Nasci<sup>×</sup>

With the signing of the SECAPs, European cities and municipalities are taking steps to respond to an energy problem deriving from the demand for summer air conditioning, which, since the early 2000s, has exceeded the demand for winter heating. Sustainable urban regeneration requires action by applying an integrated approach between the sectors and professional figures involved, following the principles of sustainable development. Sustainable construction focuses on reducing the environmental impact of the building industry using renewable and recyclable materials, reducing energy consumption and embodied energy of building materials. The recycling and reusing of waste materials can lead to energy savings, cost reductions, potentially improved products, and reduced waste generation-related hazards to the environment. However, an important consideration when using green construction materials as alternative raw materials is having a thorough understanding of their chemical, mineralogical, and physical properties. This knowledge is essential to ensure that recycled materials can be effectively integrated into materials production without negatively impacting the final product quality or production efficiency. We present here processes developing existing materials which are substantial to ensure the maintenance of that heritage recognized, experienced and enjoyed by the people living a given territory.

**Keywords:** global change, urban environment, building materials, building heritage and renovation

#### Introduction

The building heritage of the Second Twentieth Century, although recognized as being of cultural interest by the urban planning instrument in force, remains at risk of tampering or demolition as the community of citizens, and particularly the

<sup>\*</sup>Senior Research Associate, Institute for the BioEconomy CNR, Italy.

<sup>\*</sup>Researcher, Institute for the BioEconomy CNR, Italy.

Researcher, Institute for the BioEconomy CNR, Italy.

<sup>\*</sup>Researcher, Institute for the BioEconomy CNR, Italy.

Senior Research Associate, Institute for the BioEconomy CNR, Italy.

<sup>\*</sup>Full Professor, University of Modena and Reggio Emilia, Italy.

<sup>\*</sup>Researcher, University of Modena and Reggio Emilia, Italy.

Researcher, CERTIMAC, Italy.

<sup>\*</sup>Researcher, CERTIMAC, Italy.

properties, do not recognize its cultural value and identity. The main objective of this study is to design the possibility of intervention in this protected heritage, to increase the energy consumption mitigation and environmental adaptation character while respecting the architectural and stylistic language that distinguishes it.

The building restoration should ensure the structural and aesthetic integrity of the existing plasters to maintain their original appearance and chemical-physical characteristics. The mixture and color of the material used must be compatible with the existing ones, so it is necessary to identify an ideal mixture of plaster that does not differ from the original.

The Municipality of Bologna' Building Regulations, approved in the context of the General Urban Plan (PUG), in the "Approfondimenti conoscitivi" - Tavole dei Vincoli (and by the previous RUE in the "Disciplina dei materiali urbani" art.57). Bologna General Urban Plan recognizes, among the existing building architectural Heritage, the "buildings of interest from the Second Half of the Twentieth Century" in order to take into consideration the material and cultural Heritage matured over the last century. The cataloging has divided the built Heritage of the Twentieth Century based on a chronological criterion: the manufacts built in the period between 1915 and 1949 have been collected in the category of buildings of historical-architectural interest of the Modern, the manufacts after 1949 made up the category of buildings of cultural and testimonial interest of the Second Half of the Twentieth Century. The criterion that led to considering only a few buildings from the last century was based on the classification previously made by the PSC and on the existence of files concerning the buildings drawn up by the MiC (Ministry of Cultural Heritage of Italy) and the IBC (Institute of Cultural Heritage of Italy), which decreed their architectural quality. Furthermore, the buildings restricted by the Superintendency were added after verifying that they had been built in the reference period. It should be noted that since the construction is recent, the danger of tampering and/or demolition is particularly high, as awareness and sensitivity in this regard is left to the owners, as a regulatory limit of intervention does not currently support them. Legislative Decree 42/2004 explicitly excludes from its protection works by living authors or whose execution does not go back more than fifty years (Article 10 paragraph 5), however it seems that it can be protected through the copyright law in as a work of art, but if this law protects a subjective right. It does not seem easily usable in the context of the public interest. It is a question of activating a reflection, also of a legal-regulatory type, as well as on the definition and delimitation of the objects to be protected, on the regulatory instruments to be put in place, possibly exploring new forms that the autonomy of the local authority. This Heritage is recognized but there is no cultural perception of its presence, nor of its cultural relevance, and there is the risk of losing part of it. In fact, in this period of major interventions on the building Heritage, which generally focuses on buildings dating from the 1960s up to today, there is the risk of proceeding with "not respectful" interventions only to increase energy performance in order to respond to mitigating needs of today's city.

To address this issue, we are conducting a study in the Bolognina District (Municipality of Bologna, Italy) an analysis of the materials of the exterior vertical

walls of one building identified as of interest from the Second Twentieth Century, characterized by plaster and tiles covering. The objective is to develop cooling materials that, in addition to ensuring higher reflectivity (albedo), can respect the style and architectural language while improving the indoor and outdoor wellbeing. Such new coatings will not inhibit but rather enhance the thermo-hygrometric exchange between indoor and outdoor, ensuring the physiological well-being of the individual. A methodology is proposed below for the application of new materials with the primary objective of increasing the energy and adaptation performance of the protected building heritage of the second half of the twentieth century, guaranteeing respect for the characterizing architectural/stylistic elements and stimulating the sensitivity of the community to regard. The cool materials were studied to guarantee the high reflexivity (albedo) that characterizes them, can respect the architectural style and language and improve the outdoor well-being of buildings, and improve, if not at least keep unchanged, the indoor one. About indoors, it is understood that these new vertical packages do not alter, but rather tend to improve the thermo-hygrometric exchange between indoor and outdoor environments, guaranteeing the physiological well-being of citizens, with particular attention to the weakest groups.

#### **Materials and Methods**

#### Ceramic Tiles Characterization

Ceramic tiles are building materials that can be easily modified to become solar reflective surfaces because of their high intrinsic thermal emissivity ( $\epsilon$  = 0.90), excellent durability over time, and resistance to dirt and fouling due to a topcoat ceramic glaze. Another advantage of ceramic materials is the possibility of obtaining coloured products by ink-jet printing, allowing the fabrication of solar reflective ceramic materials with improved aesthetic characteristics (the so-called cool colours) (Cedillo-González et al. 2022, 2023). These materials present a coloured response in the visible wavelength range and higher SR values than conventional materials of the same colour. Moreover, ink-jet-derived solar reflective tiles increase customization capabilities, making it possible to restore historical buildings without compromising their architectural value.

Conventional solar reflective products are constituted by a support, a reflective basecoat, and an IR-transparent topcoat to protect the basecoat. This configuration recalls the layout of porcelain stoneware tiles, which are fabricated by a layer configuration: the ceramic support (1st layer), the engobe (2nd layer), the digital colouration (3rd layer), and the glaze (4th layer). Following this premise, several authors have designed ceramic tiles with high solar reflectance. For instance, Ferrari et al. (2013) designed glazed ceramic tiles with high solar reflectance (SR = 0.90) by adding ZrSiO<sub>4</sub> and TiO<sub>2</sub> to the engobe's formulation. As authors found that the ceramic engobe plays a crucial role in enhancing the solar reflective properties of tiles, Governatori et al. (2021) focused their attention on designing high-reflectance glass-ceramic frits, which are a critical component of the

engobe's formulation. In a second work, the same authors investigated the obtainment of solar-reflective ceramic tiles by modifying the engobe's formulation, finding that when a glass-ceramic frit with a high intrinsic SR value is incorporated into the formulation of an industrial engobe, it can raise its albedo (Governatori et al. 2022).

An additional advantage of developing white and coloured solar reflective porcelain stoneware ceramic tiles is that their production allows the incorporation of secondary raw materials (SRMs) in all of their elements: support, engobe and glaze. The use of SRM will lead to additional energy savings during the production process and a reduction of the environmental impact of the final products. However, it is known that ink-jet decoration negatively affects the albedo of tiles prepared with reflective engobes due to its coverage by the inks and their mineralogical composition (Cedillo-González et al. 2022, 2023). For this reason, the albedo of the engobe should be as high as possible to compensate for this reduction by ink-jet decoration. This work produced a set of functional solar reflective engobes using several SRMs such as recycled glasses (four types), chamotte, granite waste, and waste yttria-stabilized zirconia from term spraying processes. The obtained engobes were characterized by CIELab colour (colorimetric model), gloss, optical dilatometry and solar reflectance. Their properties were compared with a conventional engobe of similar chemical composition.

The preparation of functional solar reflective engobes was investigated in three steps using several SRMs such as recycled glasses (photovoltaic glass, screen glass, and two types of urban-derived recycled glass), chamotte, granite waste, and waste yttria-stabilized zirconia (YSZ) from thermal-spraying processes. This study aimed to develop an engobe formulation with enhanced SR property, containing at least 30 wt. % of SRM. First, we conducted a preliminary study where a conventional frit-containing engobe (labelled here as "ESTD") made of conventional raw materials (RM) was modified by replacing 100% of the frit with several types of recycled glass. Additionally, 100% of the quartz and the K feldspar were substituted by chamotte and granite waste, respectively. The second step consisted of the modification of the previous engobe's formulations to reduce as much as possible the total molar content of TiO<sub>2</sub> and Fe<sub>2</sub>O<sub>3</sub>, as these oxides promote the development of yellow colouration, negatively affecting the SR property. Modifications were performed only for two formulations (as the others were already set at the minimum possible TiO<sub>2</sub> and Fe<sub>2</sub>O<sub>3</sub> content) using the software Glaze Master® (Expert System Solutions, Modena, Italy). The third step consisted of adding 5 wt.% or 10 wt.% of a whitening agent in the engobe's formulations that presented the best colour ( $L^* = \text{brightness}$ ), high SR property, and an adequate content of SRM. The aim was to further enhance the SR in anticipation of a reduction of this property when the ink-jet inks cover the engobe during the production of porcelain stoneware tiles (support + engobe + ink-jet decoration + glaze). The whitening agent is an SRM composed of waste YSZ from thermal-spraying processes. Here, the formulations of two selected engobes (those with the best properties) are presented in Table 1, where the number in the formulation's name represents the molar % of TiO<sub>2</sub> and Fe<sub>2</sub>O<sub>3</sub> (the sum of the two

oxides) that was reduced. The number after the term "Zr" in the formulation's name represents the wt. % of waste YSZ that was added.

**Table 1.** Formulations (Expressed as wt.%) of the Selected Functional Solar

Reflective Engobes

| RM or SRM     | ESTD  | EGW27Zr10<br>(Formulation 1) | EMG14Zr5<br>(Formulation 2) |

|---------------|-------|------------------------------|-----------------------------|

| Na feldspar   | 20.00 | 18.17                        | 41.65                       |

| K feldspar    | 20.00 | -                            | -                           |

| Clay 1        | 15.00 | -                            | -                           |

| Whitening 1   | 8.00  | 3.91                         | 6.05                        |

| Clay 2        | 7.00  | -                            | 7.93                        |

| Kaolin        | 14.00 | 31.96                        | 22.99                       |

| Whitening 2   | 8.00  | 7.33                         | 7.92                        |

| Quartz        | 4.00  | 0.82                         | 0.78                        |

| Frit          | 4.00  | 4.75                         | -                           |

| Granite waste | -     | 23.05                        | 5.04                        |

| Mixed glass   | -     | -                            | 2.63                        |

| Waste YSZ     | -     | 10.00                        | 5.00                        |

All engobes were prepared according to a standard laboratory protocol. For each formulation, a mixture of 200 g of dry raw and secondary raw materials was placed in a 300 mL porcelain jar, along with 250 g of sintered alumina grinding bodies, 0.3 g of tripolyphosphate, 0.3 g of slurry modifier, and 84 g of tap water. A rapid mill was used to create a consistent slurry from the mixture, with a milling duration of 40 minutes. Two types of specimens were prepared: engobed porcelain stoneware tiles and 40 mm (Ø)-disks of pure engobes. The engobed tiles were used to measure the solar reflectance, gloss and colour (CIELab) properties of the engobes, while the disks-shaped specimens were useful to determine the thermal expansion coefficient ( $\alpha$ ) by optical dilatometry and the shrinkage. To prepare the engobed tiles, the density of the slurry was measured using a 100 mL steel pycnometer and adjusted to a value of 1.65 g/ml. The slurry was then precisely deposited on conventional and fired porcelain stoneware substrate, humidified using an airbrush, with a 0.6mm engobe thickness. The engobed tiles were fired in an industrial kiln utilizing a 50-min cold-to-cold firing cycle suitable for porcelain stoneware, with a maximum temperature of 1205 °C. The remaining mixture was dried at 110 °C for 12 h and ground with a porcelain mortar. The powdered engobes were humidified to 6 wt. % in a closed system for at least 24 h and then pressed at 30 bar to obtain the disk-shaped pressed specimens. After drying at 110 °C for 1 h, the pressed engobes were thermally treated in a laboratory furnace at 10 °C/min up to 1205 °C. An isotherm of 10 min was performed, and the engobes were naturally cooled inside the furnace. The shrinkage of the fired-pressed engobes was measured using a calliper with 0.01 mm resolution.

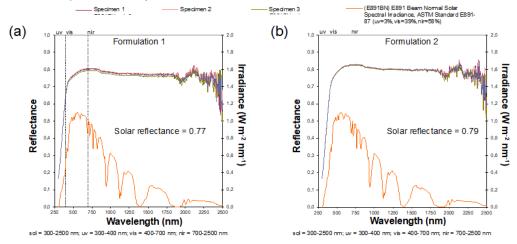

The brightness parameter  $(L^*)$  is a significant value that can be related to the SR property: high values usually correspond to high SR. Figure 1 presents the solar reflectance spectra of the selected engobes (3 specimens were measured) from which the solar reflectance (SR) values (presented in Table 2) were calculated.

**Figure 1.** Solar Reflectance Spectra of the Selected Engobes from which the Solar Reflectance (SR) Values Were Calculated. (a) Formulation 1 (EGW27Zr10). (b) Formulation 2 (EMG14Zr5)

**Table 2.** Technological and Aesthetic Properties of the Standard and Selected Engobes

| Formulation   | %    | Shrinkage (%)    | α/1 × | Gloss  |        | Colour     |            | SR          |

|---------------|------|------------------|-------|--------|--------|------------|------------|-------------|

| Formulation   | SRM  | Sili likage (70) | 107   | (60°)  | $L^*$  | a*         | <i>b</i> * | SK          |

| ESTD          | 0.0  | $9.52 \pm 0.01$  | 41.36 | 2.50 ± | 89.3 ± | $0.39 \pm$ | 5.58 ±     | $0.769 \pm$ |

| ESID          | 0.0  | 9.32 ± 0.01      | 41.30 | 0.00   | 0.1    | 0.04       | 0.04       | 0.001       |

| Formulation 1 | 33.1 | $8.8 \pm 0.2$    | 44.15 | 2.43 ± | 89.7 ± | 0.13 ±     | 2.18 ±     | $0.771 \pm$ |

| Formulation 1 | 33.1 | 6.6 ± 0.2        | 44.13 | 0.06   | 0.3    | 0.04       | 0.07       | 0.007       |

| Formulation 2 | 12.7 | $8.65 \pm 0.09$  | 45.11 | 2.40 ± | 88.9 ± | 0.61 ±     | 5.09 ±     | $0.794 \pm$ |

| Formulation 2 | 12.7 | 6.05 ± 0.09      | 43.11 | 0.00   | 0.3    | 0.02       | 0.05       | 0.002       |

The selected engobe formulations with reduced molar % of TiO<sub>2</sub> and Fe<sub>2</sub>O<sub>3</sub> and containing 5 and 10 wt. % of the SRM waste YSZ (EGW27Zr10 and EMG14Zr5) present a slightly higher solar reflectance than the standard engobe. This reduced increase in the SR property is likely due to the use of SRM, which intrinsically contains some impurities in their chemical compositions, and those impurities can act as solar radiation absorbers in the final material. Additionally, it is worth mentioning that these formulations can be further improved to increase both the SR and the wt.% of SRM, as the conventional whitening agent and the zirconia raw materials can be further replaced using waste YSZ.

Table 2 presents a selection of the most significant technological and aesthetic properties of the engobes produced in this work. Shrinkage and thermal expansion properties are essential to setting the proper firing conditions for porcelain stoneware tiles. The materials' thermal properties should be compatible with ceramic support and the glaze to avoid deformation or crack formation. On the other hand, gloss and colour are two essential properties that increase the possibilities of industrial application and commercialization of the produced engobes in zero environmental impact buildings and constructions. Notably, in the era of ceramic ink-jet printing, high-quality decorations require engobes with high whiteness and opacity to allow the advantages of ink-jet decoration: the modification in real-time of the decoration patterns, the use of shorter times to change drawings and colours, the opportunity to perform easier testing at lower

costs, the increased ability of customization options, the possibility to perform edge-to-edge prints or decorate relief surfaces and a drastic reduction of the amounts of inks compared with the quantities used by traditional decoration systems (Cedillo-González et al. 2022). Table 2 shows that most of the selected engobes present a lower shrinkage value than the standard engobe. The engobes' thermal expansion coefficient ( $\alpha$ ) in the 50 °C – 400 °C interval was measured using the pressed samples. It was found that the produced engobes present  $\alpha$ values comparable to that of the standard engobe. The gloss of the engobes was measured on the fired tiles. It is worth noticing that incorporating several SRMs in the engobe formulation does not significantly affect the opacity of the engobes, as the samples presented gloss values comparable to those presented by the standard engobe. The colour was also measured on the fired tiles using the CIELab colour space. As in the case of gloss, incorporating several SRM in the engobe formulation does not significantly affect the colour of the engobes, as most of the samples present  $L^*$ ,  $a^*$  and  $b^*$  values comparable to those presented by the standard engobe. Therefore, from the previous results, an important conclusion was derived: an urban-derived mixed recycled glass, granite waste and waste YSZ can be used to modify industrial ceramic engobes formulated with conventional RM without losing the aesthetic characteristics of the engobe.

#### Built Environment Characterization

The building under study (44°30′50.9" N, 11°20′49.7" E) was the former neighbourhood library (Biblioteca Pelagalli), then nursery school until 2012 – current headquarters of Hex, a coworking association, privately owned and was designed in the year '70 by the Architect designer Lorenzino Cremonini (1939-2014) (Figure 2). A microclimate and fluid dynamics analysis of the current context carried out with the ENVImet model during a day characterized by a heat wave, to understand the vulnerabilities present in the vicinity of the building under study. ENVI-met is a three-dimensional non-hydrostatic microclimate model designed to simulate the surface-plant-air interactions within daily cycles in the urban environment with a typical resolution of 0.5 to 10 m in space and 10 sec in time. Several variables can be simulated, included flow around and between building, exchange processes of heat and vapor at the ground surface and at the walls, turbulence exchanges, vegetation parameters, bioclimatology and particle dispersion (ENVI-met, Bruse and Fleer 1998).

A collection of data regarding the construction methods and previous interventions on the historic building and a survey in situ to collect samplings of the coatings (ceramic tiles and plaster) of the vertical masonry packages have been performed. Subsequently, a chemical analysis and mineralogical characterization of the collected material that makes up the package, with particular attention to the external coating was conducted by University of Modena and Reggio Emilia and CERTIMAC.

The new type of coating was studied to guarantee high reflectivity (cool material) and a good response to urban air pollution, even at this stage of the study limited to an increase of 10% of the surface albedo property. Thus, the new building project was characterized by an external vertical cladding made of ceramic tiles highly performing both in terms of reflectivity, sustainability, and resistance to atmospheric pollution.

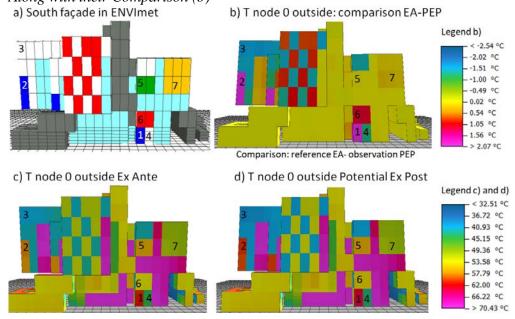

A microclimate and fluid dynamics analysis of the project status of the building with the ENVImet model, with 1x1 m<sup>2</sup> horizontal resolution, has been conducted to assess in detail the foreseen effects of the new materials.

Figure 3 reports the actual configuration and condition of the investigated building. It is possible to note that the structure has a public or private commercial destination, but not as residential housing. As previously described, the construction period will see in the housing policies of the city of Bologna the need to combine the availability of housing with that of the development of buildings that act as a point of aggregation and socialization of the population.

This building, due to its particular architectural composition, was the object of admiration or strong criticism in those years, because it inserted a strong innovative drive into the city landscape by drawing on other European experiences. This was not an isolated episode, with the passage of time also in other places (for example Milan, Italy) this new building method became increasingly established, and today it constitutes a large part of the cultural heritage of the entire nation's buildings.

**Figure 3.** The Former Neighbourhood Library (Biblioteca Pelagalli), then Nursery School until 2012 – Current Headquarters of Hex, a Coworking Association, Privately Owned

Table 3 reports the model input data of physical properties for the real tiles (Ex Ante, EA), the simulation performed by changing only the albedo values of tiles incrementing it by a 10% (Ex Post only Albedo, EPA), and the input data of the expected physical characteristics of the new tiles also incremented of 10% in the albedo values and imposed the new emissivity values at 0.90 for all the tiles of various colours (Ex Post Potential, PEP).

This numerical experiment was conducted to verify whether the modification of the albedo alone, which could be carried out with a mere surface treatment, can lead to differences of significant value for the surface temperature, or whether deeper modifications to the structure of the tiles are essential to obtain the desired effects.

**Table 3.** Physical Properties Characterizing the External Walls of Biblioteca Pelagalli for Ex Ante (EA), Ex Post Only Albedo (EPA), and Potential Ex Post (PEP) Configurations

| EA                     | Red   | Yellow | Orange | Green | Blue  | White |

|------------------------|-------|--------|--------|-------|-------|-------|

| Absorption (shortwave) | 0.575 | 0.420  | 0.510  | 0.680 | 0.800 | 0.236 |

| Reflection (shortwave) | 0.425 | 0.580  | 0.490  | 0.320 | 0.200 | 0.764 |

| Emissivity             | 0.906 | 0.889  | 0.900  | 0.887 | 0.906 | 0.879 |

Vol. 11, No.3 Georgiadis et al.: A Methodological Proposal for the Characterization...

| Specific heat [J/(kg*K)]       | 770        | 770        | 770        | 770        | 770        | 770        |

|--------------------------------|------------|------------|------------|------------|------------|------------|

| Thermal conductivity [W/(m*K)] | 1.072      | 1.072      | 1.072      | 1.072      | 1.072      | 1.072      |

| Density [kg/m3]                | 2277.30005 | 2169.89990 | 2207.30005 | 2070.89990 | 2284.00000 | 2198.89990 |

| EPA                            | Red        | Yellow     | Orange     | Green      | Blue       | White      |

| Absorption (shortwave)         | 0.532      | 0.360      | 0.460      | 0.640      | 0.770      | 0.160      |

| Reflection (shortwave)         | 0.468      | 0.640      | 0.540      | 0.360      | 0.230      | 0.840      |

| Emissivity                     | 0.906      | 0.889      | 0.900      | 0.887      | 0.906      | 0.879      |

| Specific heat [J/(kg*K)]       | 770        | 770        | 770        | 770        | 770        | 770        |

| Thermal conductivity [W/(m*K)] | 1.072      | 1.072      | 1.072      | 1.072      | 1.072      | 1.072      |

| Density [kg/m3]                | 2277.30005 | 2169.89990 | 2207.30005 | 2070.89990 | 2284.00000 | 2198.89990 |

| PEP                            | Red        | Yellow     | Orange     | Green      | Blue       | White      |

| Absorption (shortwave)         | 0.532      | 0.360      | 0.460      | 0.640      | 0.770      | 0.160      |

| Reflection (shortwave)         | 0.468      | 0.640      | 0.540      | 0.360      | 0.230      | 0.840      |

| Emissivity                     | 0.900      | 0.900      | 0.900      | 0.900      | 0.900      | 0.900      |

| Specific heat [J/(kg*K)]       | 600        | 600        | 600        | 600        | 600        | 600        |

| Thermal conductivity [W/(m*K)] | 1.100      | 1.100      | 1.100      | 1.100      | 1.100      | 1.100      |

| Density [kg/m3]                | 2250       | 2250       | 2250       | 2250       | 2250       | 2250       |

#### **Results and Discussion**

The building was represented, in the three cases (EA, EPA, PEP) (EA), without the buildings actually present in its surroundings in order to see the maximum effect of the albedo variation. It was decided to maintain the vegetation close to the north façade in order to verify its possible influence. The most detailed cell resolution in ENVI-met is  $1x1 \, \text{m}^2$ . Because of the complex chromatic design developed with the tiles that characterizes the building's facades, a simplification was necessary also to represents all the colours present in each single façade.

In Table 4 are reported the values of the wall temperatures obtained in EA, EPA, and PEP simulations for each colour tile in south façades. In the specific case of our simulation, a wish-list was adopted on the physical properties of the materials which unified the density values at 2250 kg/m<sup>3</sup> and increased the thermal conductivity for all from 1,072 to 1,100 W/mK. Furthermore, the emissivity values were standardized to 0.9.

**Table 4.** Outside Wall Temperature Values Obtained by Envi-met Simulation for Ex Ante, ex post Only Albedo, and Potential Ex Post Scenarios for Each Colored Tile

| Hour         | Parameter         | Facade and color tile | EA       | EPA      | Comparison<br>EA-EPA | PEP      | Comparison<br>EA-PEP |

|--------------|-------------------|-----------------------|----------|----------|----------------------|----------|----------------------|

| 2:00<br>p.m. | T wall outside    | Sud-blue (1)          | 61.71 °C | 60.74 °C | - 0.97 °C            | 64.29 °C | 2.58 °C              |

| 2:00<br>p.m. | T wall outside    | Sud-blue (2)          | 58.32 °C | 57.41 °C | -0.91 °C             | 60.58 °C | 2.25 °C              |

| 2:00<br>p.m. | T wall outside    | Sud-white (3)         | 40.78 °C | 38.41 °C | -2.37 °C             | 39.19 °C | -1.59 °C             |

| 2:00<br>p.m. | T wall outside    | Sud-white (4)         | 45.10 °C | 42.61 °C | -2.49 °C             | 43.89 °C | -1.21 °C             |

| 2:00<br>p.m. | T wall<br>outside | Sud-green (5)         | 56.74 °C | 56.64 °C | -0.10 °C             | 56.80 °C | 0.06 °C              |

| 2:00<br>p.m. | T wall outside    | Sud-red (6)           | 53.55 °C | 52.22 °C | -1.33 °C             | 54.78 °C | 1.22 ℃               |

| 2:00<br>p.m. | T wall outside    | Sud-orange (7)        | 49.99 °C | 48.49 °C | -1.50 °C             | 50.23 °C | 0.24 °C              |

While maintaining the same structural characteristics for the tiles, and changing only the albedo increasing it by 10%, the decrease in the surface temperatures is well evidenced for all the various colours, for the simulation where the physical properties were changed a very different behaviour have been obtained.

The outside wall temperature of improved blue tile at 2 p.m. shows a higher surface temperature (up to 2.58 °C). This can be explained throughout Figure 4 that shows that the tile 1 is very close to the surface so, probably, it is influenced by the radiant temperature emitted by the floor. The other blue tile (2 at 6m height) shows an increment of 2.25°C.

The white tile is the only one that shows an effective cooling of the wall of about -1.59°C near the walking surface and -1.21 °C at about 11 m height. The green tile does not show differences in the wall temperature (0.06 °C) while the red tile shows a warming of the wall surface (1.22 °C).

Some of these results for EA and PEP comparison appear to be counterfactual, that is, the current result appears to conflict with what was reasonably expected. In Figure 4 is reported the complexity of the facade in terms of tile colouring is reported. However, in our modelling simplification we have included the characteristics on the ground coverage and, therefore, the simulation is also

affected by this contribution, which differs at different heights of the building. This turns out to be a confounding effect on the results which would require an analysis in the laboratory, in controlled conditions, a turning point developed tiles trying to magnify the effects without however exceeding in the performances the current limitations foreseen by the urban regulations, such as for example those linked to potential glare effects at the street level. Thus, the evaluation work is still ongoing in parallel to the lab development of the new materials and will be followed through other deliverables within ECOSISTER Programme. From the same case study, the ageing effects of the ceramic tiles will be evaluated, to aid advising the industrial production on increasing materials resilience for weathering and air pollution in an urban context.

**Figure 4.** Composition of the South Façade of the Building (a) and the Outside Wall Temperature Obtained by the Model for EA (c) and PEP (d) Simulations Along with their Comparison (b)

What clearly emerges from the simulation is that the renovation of the tiles in buildings belonging to the cultural heritage needs detailed studies on the structural composition of the materials, as their physical properties, if not carefully calibrated, can give rise to effects that conflict with the desired results.

#### **Conclusions**

From the comparison made, the thermal excursion of PEP tiles in the temperature on the facade leads to a range of approximately 4.5 °C. The change in the albedo of the material can influence the thermal regime of the building but is not possible to evidence an effect on the well-being outdoor, except for possible glare phenomena which can cause high albedo values of the surfaces, including walls. Furthermore, it was found that the variation of the albedo alone produces

very small effects already at a superficial level and, therefore, significant effects on the outdoor environment is reasonable to exclude, even possible research developments may concern new simulations in ENVI-met gradually increasing the albedo to understand the most performing threshold values for each colour, to be able to give indications to the production sector.

At present, utilising the simulated values for the potential new tiles a limitation to only 10% in the albedo value it is debatable it can influence significantly the outdoor environment, as other authors already pointed out, even more studies are necessary to understand if the internal building energy consumption will be positively affected by the innovation (Fabbri et al. 2020, Lopez-Cabeza et al. 2022). As Lee and Mayer (2018) clearly outlined, higher albedo of the building walls causes an increase of mean air temperature and mean irradiance temperature, influencing the PET (Physiologically Equivalent Temperature) values, thus reflecting in a certain decrease of outdoor comfort (Matzarakis et al. 1999). While the increase in indoor thermal comfort is uncontroversial, the effects on the outdoor thermal values has to be specifically investigated case by case.

In our modelling experiment, some limitations to the performed modelling study are due to the oversimplification of the external fabric texture (i.e. surrounding buildings and pavements). As reported in Fabbri et al. (2020), the role of paved surfaces has a much more relevant influence on external comfort compared to the one due to the facades. However, the latter must be part of an overall review of the entire urban regeneration system, because it can provide a contribution, even if limited but, above all, it can contribute to preserving the identity of the places and the value system of the cultural heritage of the resident population.

#### Acknowledgments

This study was funded by Ecosystem for Sustainable Transition in Emilia-Romagna (Ecosister). Progetto PNRR Programma di Ricerca e Innovazione – CODE ECS0000003 NextGenerationEU, Piano Nazionale di Ripresa e Resilienza (PNRR) – Missione 4 Componente 2.

#### References

Bologna General Urban Plan. Available at: http://dru.iperbole.bologna.it/pianificazione/profilo-e-conoscenze-approfondimenti-conoscitivi. [Accessed 4June 2024]. (In Italian).

Bruse M, Fleer H (1998) Simulating surface-plant-air interactions inside urban environments with a three-dimensional numerical model. *Environmental Modelling and Software* 13(3–4): 373–384.

Cedillo-González EI, Governatori M, Ferrari C, Siligardi C (2022) Solar reflective ink-jet printed porcelain stoneware tiles as an alternative for Urban Heat Island mitigation. *Journal of European Ceramic Society* 42: 707–715.

- Cedillo-González EI, Governatori M, Siligardi C (2023) Highly reflective engobes for inkjet printed coloured porcelain stoneware tiles (CO-2:L05). *Ceramics International* 49(14-PART B): 24259–24267.

- ENVI-met. Available at: http://www.envi-met.com/. [Accessed 4 June 2024].

- Fabbri K, Gaspari J, Bartoletti S, Antonini E (2020) Effect of facade reflectance on outdoor microclimate: an Italian case study. *Sustainable Cities and Society* 54: 101984.

- Ferrari C, Libbra A, Muscio A, Siligardi C (2013) Design of ceramic tiles with high solar reflectance through the development of a functional engobe. *Ceramics International* 39(8): 9583–9590.

- Governatori M, Ferrari C, Manfredini T, Siligardi C (2021) Preparation and characterization of glass ceramic frits with high solar reflectance. *Open Ceramics* 6(Jun): 100091.

- Governatori M, Cedillo-González EI, Manfredini T, Siligardi C (2022) Solar reflective properties of porcelain tiles for UHI mitigation: effect of highly reflective frits in the engobe's formulation. *Materials Today Sustainability* 20(Dec): 100255.

- Lee H, Mayer H (2018) Thermal comfort of pedestrians in an urban street canyon is affected by increasing albedo of building walls. *International Journal of Biometeorology* 62(7): 1199–1209.

- Legislative Decree 42/2004. Available at: https://www.bosettiegatti.eu/info/norme/statali/2004\_00 42.htm. [Accessed 4 June 2024]. (In Italian).

- Lopez-Cabeza VP, Alzate-Gaviria S, Diz-Mellado E, Rivera-Gomez C, Galan-Marin C (2022) Albedo influence on the microclimate and thermal comfort of courtyards under Mediterranean hot summer climate conditions. *Sustainable Cities and Society* 81: 103872.

- Matzarakis A, Mayer H, Iziomon M (1999) Applications of a universal thermal index: physiological equivalent temperature. *International Journal of Biometeorology* 43: 76–84.

# Self-locking Domino Logic Pipelined Controller for RISC-V in FPGA

By Florian Deeg\*, Xiangyuan Wu<sup>±</sup> & Sebastian M. Sattler°

This paper proposes an asynchronous RISC-V CPU design based on selflocking domino logic. The asynchronous approach offers advantages over traditional synchronous designs, including improved performance, lower power consumption, and greater modularity. The paper details the design and implementation of the asynchronous control unit using domino logic on an FPGA development board. The control unit is designed for a Turing-complete 32-bit RISC-V architecture. A significant aspect of the design is the self-locking mechanism, which ensures that the circuit only unlocks after all processing stages have been completed. This eliminates the need for a global clock and simplifies hazard-free operation. Furthermore, the paper discusses the potential for parallelizing the ALU using domino logic to improve performance further. The implementation of the asynchronous CPU has been analyzed in terms of power, performance, and area using the Vivado Design Suite. The power analysis indicates that the asynchronous processor consumes considerably less power in the clock network compared to its synchronous counterpart, thereby underscoring its energy efficiency. A performance analysis using the SPECint2000 benchmark suite demonstrates a 10% increase in performance, while only using slightly more area. These findings illustrate the asynchronous processor's potential for performance-critical applications while maintaining energy and area efficiency.

Keywords: domino logic, asynchronous design, self-locking, RISC-V, GALS

#### Introduction

Synchronous circuits represent the state of the art in circuit design. Still, asynchronous circuits are becoming increasingly important as they offer numerous advantages over synchronous circuits (performance, power consumption, modularity, no single-point-of-failure, no clock skew, etc.) (Sparsø 2001). Asynchronous circuits are also more resilient to fluctuations in the supply voltage and temperature. Local faults in asynchronous designs are often limited to the affected area, which increases fault tolerance. Furthermore, they generate less electromagnetic interference and are therefore more suitable for applications in which electromagnetic compatibility (EMC) plays an important role (Bouesse et al. 2007). However, the advantages of this approach are also offset by disadvantages, including the necessity for more complex design methods and an associated lack of design tools.

Field Programmable Gate Arrays (FPGAs) are a special hardware component distinguished by their high performance, flexibility, and energy efficiency. In

<sup>\*</sup>PhD Student, Friedrich-Alexander-University Erlangen, Germany.

<sup>&</sup>lt;sup>±</sup>Student, Friedrich-Alexander-University Erlangen, Germany

Professor, Friedrich-Alexander-University Erlangen, Germany.

contrast to conventional integrated circuits (ICs), which are pre-programmed for a specific function, FPGAs can be reconfigured after manufacture to undertake new tasks or optimize performance. This feature renders them an optimal platform for the development of demanding applications that require high computing power, low latency, and customizability.

For a considerable period, the market for processors was divided between two architectures: x86 and ARM, which are mainly used in mobile devices. In recent years, however, a new player has joined them and is providing a breath of fresh air in the form of RISC-V. RISC-V is a license-free instruction set architecture (ISA) that originated at the University of California, Berkeley (Waterman 2016). In contrast to x86, which has grown historically and is complex, RISC-V was developed from scratch. The principle of simplicity was prioritized. This simplicity is intended to minimize hardware costs on the one hand and increase flexibility on the other. RISC-V is becoming increasingly important in the processor world. One decisive factor is that it is license-free. This enables various companies and research groups to develop and utilize processors based on RISC-V. This has led to a wide variety of RISC-V processors that are used in different areas. The spectrum ranges from energy-efficient devices in the Internet of Things (IoT) to highperformance computers. Although RISC-V has not yet reached the market share of x86 and ARM, its growth potential should not be underestimated. The simplicity, flexibility, and license-free nature of RISC-V make it an attractive option for many developers. Other positive aspects of RISC-V include its energy efficiency, scalability, and security, as the basic architecture of RISC-V is so simple and offers little scope for attack.

#### Structure of the Paper

A brief literature review is conducted to distinguish this paper from others in the field. The following section presents the circuit structure, which comprises the self-locking pulse circuit, the dual-rail domino logic circuit, and the entire pipeline with completion detection and its realization in the FPGA. Subsequently, an existing synchronous multicycle RISC-V processor is briefly introduced, after which a control automaton for this Turing-complete processor is realized as a domino logic pipeline. It demonstrates how the pipeline can be utilized to control a globally asynchronous locally synchronous (GALS) system that can be arbitrarily divided into subcircuits to achieve the highest possible speed and safety. The subsequent chapter deals with the results and a comparison with synchronous automata. Finally, a conclusion and future work are presented.

#### **Related Work**

Dooply and Yun (1999) presented a method for optimizing clocking in selfresetting domino pipelines. This method employs soft synchronizers and roadblocks to allow time borrowing, thereby maximizing throughput and eliminating latch overhead. The authors introduced a high-performance clocking methodology for self-resetting domino pipelines that optimizes the clock rate through time borrowing and robust handling of clock skew while eliminating latch overhead. However, their approach does not adequately simplify the complex clocking and synchronization management or provide a robust precharge management system, nor does it adequately simplify the complex clocking and synchronization management or provide a streamlined implementation and testing methodology. Jung et al. (2002) presented a high-speed add-compare-select (ACS) unit for Viterbi decoders using locally self-resetting CMOS (SRCMOS), which achieves significantly higher data rates compared to static and domino CMOS designs. This approach is associated with higher power consumption and increased design complexity due to the need for careful device sizing and additional components. In contrast, Jung et al. (2003) introduced a dual keeper structure and delay logic gates to enhance the performance and noise margin of domino logic gates, ensuring high-speed switching and robustness to noise and timing variations. However, their approach introduces additional design complexity and lacks a focus on scalability issues

In (Litvin and Mourad 2005) they presented the development of dual-rail self-resetting logic gates with input disable (DRSRLID) for fast and power-efficient arithmetic operations. They also demonstrated the application of these gates in a 16-bit parallel adder. However, their work primarily focuses on arithmetic circuits and does not extensively validate the logic in broader applications or address implementation complexity.

Alsharqawi and Einioui (2006) proposed two novel synchronization approaches for clockless pipelining of coarse-grain datapaths using self-resetting stage logic (SRSL) to achieve high throughput. The approach suffers from scalability issues and increased implementation complexity. Ramadass et al. (2014) introduced the Self Resetting Logic with Gate Diffusion Input (SRLGDI) technique to create lowpower, high-speed logic circuits and demonstrated its effectiveness through the design and simulation of various adders. However, their approach increases transistor count and design complexity. The method of designing high throughput and ultralow power asynchronous domino logic pipelines based on a constructed critical data path was introduced in (Xia et al. 2015). However, their approach does not fully address the challenges of design automation, placement, routing optimization, and timing verification. The implementation of low-power and high-performance asynchronous dual-rail interconnect using domino logic gates in 16-nm technology was proposed in (Rezaei and Moghaddam 2016). The integration of self-locking mechanisms or the detailed implementation of a complete RISC-V pipeline controller remains an issue. Sokolov et al. (2020) introduced a novel framework for automating the design of asynchronous logic control in AMS electronics, integrating formal verification and specialized analog-to-asynchronous interface components for handling non-persistent signals. It does not fully address the challenges of comprehensive design automation and efficient handling of nonpersistent signals within the FPGA implementation. Li et al. (2021) presents a methodology for implementing asynchronous phase-decoupled circuits using traditional electronic design automation (EDA) tools. The authors present an

asynchronous RISC-V processor implemented on the Xilinx ZCU102 FPGA, achieving a threefold improvement in dynamic power efficiency compared to its synchronous counterpart, while maintaining similar resource utilization. The approach demonstrates the potential of asynchronous design in reducing power consumption for IoT and neuromorphic applications, despite challenges in commercial tool support.

This work builds on the work in (Deeg and Sattler 2024), which focused on structural feasibility in the FPGA. In this paper, the design of the automaton and in particular the low-level design is described in more detail, with results of the asynchronous implementation.

#### **Self-locking Domino Logic**

This section presents the structure and realization of the self-locking domino logic in the FPGA. The delay-insensitive domino logic was selected to minimize constraints in the design process while maintaining hazard-free and race-free operations. This approach contrasts with one-step designs (Deeg et al. 2020), where complex algorithms are employed to construct the automaton without clocking. The programming in the FPGA occurs at the lowest level of abstraction to ensure that the structure is built in the same way, without the software attempting to optimize the structure. This is because the synchronous optimization process is used to build the structure. The asynchronous design cannot be simulated, so it must be built in accordance with the structure and verified with tests. This is to ensure that any known error models are excluded. The structural comparison of domino logic on the FPGA was conducted in (Deeg and Sattler 2024). This section will subsequently discuss the individual realizations in the FPGA at the low level.

#### Globally Asynchronous Locally Synchronous (GALS)

GALS is a design methodology for electronic circuits. It addresses the challenge of ensuring safe and reliable data transfer between independent clock domains within a system. A GALS system breaks down the circuit into independent blocks, each with its own local clock. These blocks communicate with each other asynchronously using handshaking protocols (Krstic et al. 2007). This allows for flexibility because blocks can operate at different speeds based on their needs, and scalability because the system can be easily expanded without worrying about the global clock. Furthermore, the GALS methodology results in reduced power consumption, as only active blocks are clocked, thereby increasing the system's power efficiency.

#### Asynchronous Handshake Protocol:

An asynchronous handshake protocol represents a communication agreement between two or more entities that allows them to exchange data without the necessity of a common clock (Chapiro 1984). In contrast to synchronous protocols, which rely on the timing of a common clock to regulate communication, asynchronous handshake protocols employ a pair of signals to regulate data transmission. The initial signal is used to initiate the transmission of data (REQ), while the subsequent signal is utilized to confirm the successful completion of the data transmission (ACK).

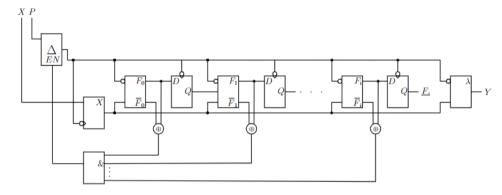

#### Pulse Circuit

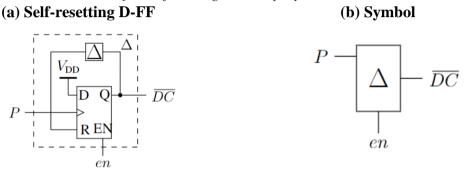

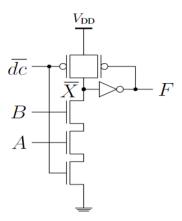

The purpose of self-locking is to enable the system to be unlocked again only once the circuit branches have been run through once and brought into a valid state. The input pulse circuit, which locks the input, can be seen in Figure 1.

**Figure 1.** Pulse Circuit for Self-locking and Duty Cycle

The self-resetting input pulse circuit is employed for self-locking, whereby the input is directly locked following an initial pulse (REQ), and a precharge phase for the domino logic is initiated by the circuit's self-resetting feedback, subsequently disabling the input. The duration of the self-reset determines the length of the precharge phase. It is therefore necessary to ensure that the precharge phase is long enough for all internal nodes to be pulled to  $V_{DD}$ . Once this has been achieved, the dual-rail domino logic gates (DRDL) have no disjunctive outputs and then trigger the evaluation phase after the system has self-reset. The rising edge of dc then initiates the transfer of states and input signals to a D-FF at the input, where they are stabilized until the next evaluation phase. The circuit thus blocks the input, generates a duty cycle, and ensures stable signals during the evaluation step. Once the following block is done it will set an enable signal to 1 (ACK) and unlock the input again.

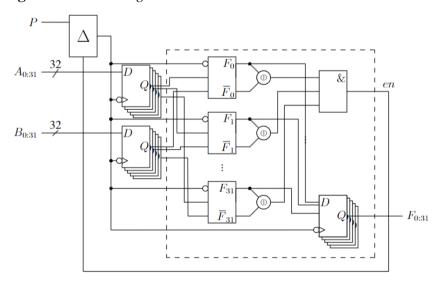

Domino Logic

**Figure 2.** Single Rail Domino Logic on Transistor Level (TL)

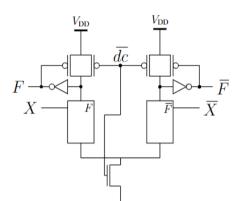

The domino logic is an asynchronous logic family based on the principle of the domino effect (Hodges et al. 2004). The domino effect describes the chain reaction that occurs when one domino falls and knocks over the next in a row. In domino logic, these effects are used to transmit data through a switching network. Domino logic offers the aforementioned advantages of asynchronous circuits over traditional synchronous logic families. The general mode of operation of a domino logic gate can be divided into two phases; precharge and evaluate. A domino gate represents the fundamental unit of construction in domino logic. It is composed of two transistor circuits, one for the pull-up phase and one for the pull-down phase, which is composed into a single unit, see Figure 2, where an example for an AND2 domino gate is given. In the precharge phase, the inner node is charged to  $V_{DD}$ , and the logic state after the inverter is 0. If we then switch to the evaluate phase, i.e. our duty cycle switches from 0 to 1, the node is pulled to GND when the Pull-Down is active (i.e., the equation is fulfilled) and logic 1 is present at the output. Domino logic gates can now be connected in series and propagate through the pipeline. As the goal is to design asynchronously and recognize the transition through the gate, DRDL gates are employed, see Figure 3. These have an output Fand the complementary output  $\overline{F}$ . The same principle applies here: first comes the precharge phase and then the evaluation phase. In the PC phase, both inner nodes are pulled to  $V_{DD}$ , the outputs are equivalent in their output value of logical 0, and then in the evaluation phase, one output becomes 1, while the other remains 0 due to the disjointness. This allows for the direct recognition of whether the domino gate has finished switching or not by linking both complementary outputs with an XOR. The dual-rail circuit thus provides a means of determining whether the circuit is in a valid state (i.e., the switched state) or an invalid state (i.e., the switching process is still underway). This information is always available, allowing the user to ascertain whether the circuit is currently occupied or ready for new data.

Figure 3. Dual Rail Domino Logic

(a) DRDL on TL

#### (b) DRDL as LUT6 2 on FPGA

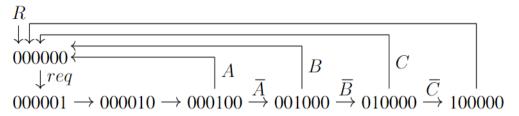

Pipeline with Completion Detection

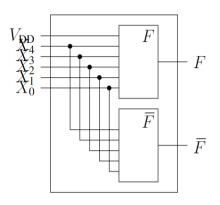

Domino gates can now be composed serially in such a way that a pipeline is created, which is operated sequentially, i.e. not pipelined. This is achieved by assigning a separate state for each transfer of a 1, i.e. each domino effect to the next stage. In principle, however, real pipelining can also be used with the corresponding holding elements between the stages. However, this would not be a viable approach for the processing of instructions and the multicycle processor in question. The serial composition is performed by setting up the dominoes from the first stage  $f_0$

to the last stage  $f_{n-1}$  to form  $f = f_{n-1} \left( f_{n-2} \left( \dots \left( f_1 \left( f_0 \right) \right) \dots \right) \right) = f_0 \circ f_1 \circ \dots f_{n-2} \circ f_{n-1}$ . Firstly, all domino gates are subjected to a preliminary charge which is designed to energize the internal nodes to a voltage of  $V_{DD}$  and set the outputs to a value of 0. The evaluation phase then pulls each DRDL gate in a path to 0, thus producing a 1 at one output of F and F. The system is then complete as soon as all DRDL gates are complementary to each other, which in turn unlocks the input. The input pulse therefore serves as a request signal and the en signal as an acknowledgment, so this is the asynchronous handshaking protocol. In the pipeline circuit, it is generally sufficient to check only the last stage for disjunctivity, as the last stage can only switch as soon as the previous one has switched. However, we have conducted a comprehensive analysis of all stages for disjunctivity, i.e. we have applied an XOR operation to each stage and rounded the results to ensure that each individual gate has switched and thus enhance safety.

#### Low-Level Primitives Design

The realization of our circuits is accomplished through the use of the Arty A7 Artix-7 FPGA Development Board, which is provided by Digilent and contains an FPGA manufactured by Xilinx Inc. The FPGA is programmed with the Vivado Design Suite (VDS) at a low-level in order to precisely define how the structures

are generated within the FPGA (what you see is what you get). The primitive libraries from ARTIX-7 (UG953 2012) are employed for this purpose. Two commands have emerged as pivotal: firstly, the ability to incorporate combinatorial loops into the constraints, and secondly, the don't touch commands to prevent the VDS from modifying any settings. The design is currently still completed manually but will be automated in the future. The logical design is based on look-up tables (LUTs). These LUTs are typically multiplexers that switch exactly one path to the output, depending on the input assignment. They are constructed in the shelf from NMOS pass transistors or transmission gates (Chiasson and Betz 2013). These low-level primitives can now be initialized as shown in the code snippet below.

**Listing 1.** Low-Level LUT6\_2 for AND2 DRDL Gate

```

LUT6 2 inst : LUT6 2 generic map (

INIT => X"800000007FFF0000") -port map (

2.

06 \Rightarrow f_{int}, -- \frac{6}{5}-LUT \text{ output } (\frac{1}{5}-bit)

3.

05 => fbar int, -- 5-LUT output (1-bit)

4.

5.

I0 => '1', -- LUT input (1-bit)

I1 => '1', -- LUT input (1-bit)

6.

7.

I2 => x_{int}(0), -- LUT input (1-bit)

8.

I3 => x_{int(1)}, -- LUT input (1-bit)

I4 => _dc, -- LUT input (1-bit)

9.

10.

I5 => '1'-- LUT input (1-bit)

11.

);

```

To realize dual-rail domino logic circuits, it has been decided that the LUT6\_2 will be employed, as this structure allows for two disjoint outputs when input 5 is clamped to  $V_{DD}$ . However, this does entail a tradeoff in that one input is no longer available for use, and the number of table entries is reduced from 26 to 25. For designs with a maximum of five inputs, however, this has no negative effects. The LUT is initialized with a hexadecimal number, in this case, the realized function is  $F = I_4 \wedge I_3 \wedge I_2 \wedge I_1 \wedge I_0$  for positive Pin F and  $\overline{F} = \overline{I_4} \vee \overline{I_3} \vee \overline{I_2} \vee \overline{I_1} \vee \overline{I_0}$  for the complementary  $\overline{F}$ . To generate the duty cycle for our self-locking input pulse circuit, a D-FlipFlop is used that is permanently connected with one at the input and briefly goes to one on the positive edge of P and resets itself asynchronously after a duration  $\tau_\Delta$ . The low-level primitive of an FDCE, which is a D-FlipFlop with Clock Enable and Asynchronous Clear, is employed for this purpose. A code snippet for our feedback pulse circuit is provided in reference to the FDCE.

#### **Listing 2.** Low-Level Self-Resetting Pulse Circuit

```

INIT => '0') -- Initial value port map (

Q => dc, -- Data output

C=> P, -- Clock input

CE => '1', -- Clock enable input

CLR => dc, -- Asynchronous clear input

D=> en -- Data input

);

```

#### Parallelization of Domino Gates

As previously stated, switching can also occur in parallel, rather than in a cascaded manner. This is because the switching processes have a clear direction and a clear end, due to the disjunctivity of the components and the self-clocking enables hazard-free operation. This is because the circuit only unlocks as soon as all the switching parts are disjoint to each other. It is therefore also conceivable, for example, to design the arithmetic logic unit (ALU) in parallel as a dual-rail domino gate to maintain the minimum processing delay by communicating with the controller using the handshake protocol and switching the individual gates in parallel until they are all disjoint. In this instance, the individual domino gates are composed in parallel to form  $f = f_0(x) + f_1(x) + ... + f_{n-2}(x) + f_{n-1}(x)$

#### Implementation for RISC-V Processor

RISC-V represents a flexible and energy-efficient alternative to the dominant Reduced Instruction Set Computer (RISC) and Complex Instruction Set Computer (CISC) architectures. The simplified instruction set at the core of RISC-V is small and orthogonal, allowing for a thriving ecosystem of innovation. This simplified approach reduces the hardware requirements and improves overall performance by eliminating the complexity and overhead associated with complex instruction sets. The paper presents the design of a control unit for a 32-bit Turing-complete RISC-V architecture.

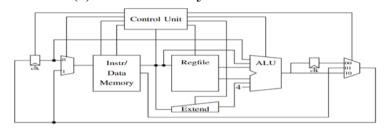

Synchronous Multicycle Central Processing Unit (CPU)

We will now briefly introduce the initial processor (Harris and Harris 2021), see Figure 4. It is a synchronous processor that is Turing complete, which means that it can calculate all Turing-computable functions. The processor is realized as a multicycle processor in order to design the different access times for different instructions in a way that allows for the division of an instruction into different individual steps. This is in contrast to a single-cycle processor, where the worst-case path for the entire instruction is considered. Instead, in this case, the worst case for the individual processing steps is considered. However, the processor employs a Harvard architecture, which is evident from the fact that it has separate data and instruction registers in a block random access memory (BRAM) (i.e., with two different addresses).

**Figure 4.** Synchronous CPU and the Synchronous State Transfer Function (a) Architecture Synchronous CPU

Synchronous Control Unit

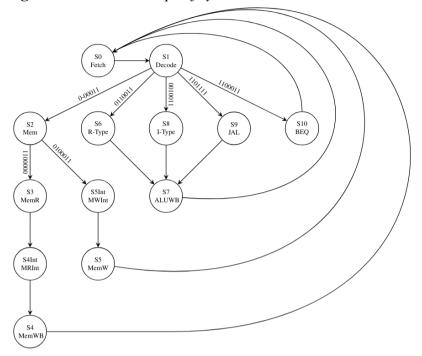

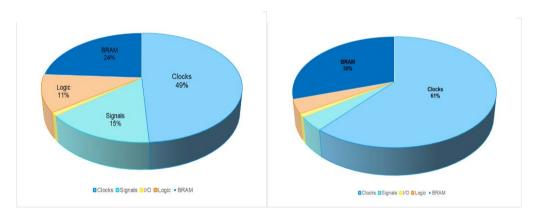

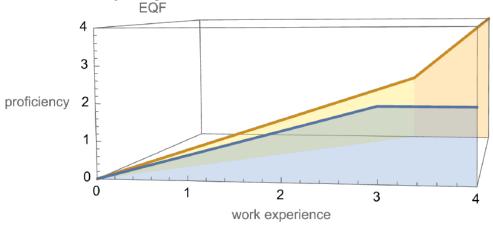

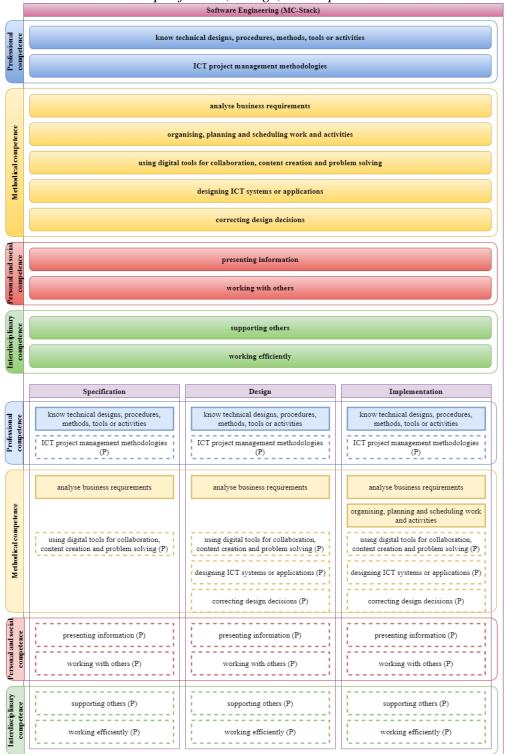

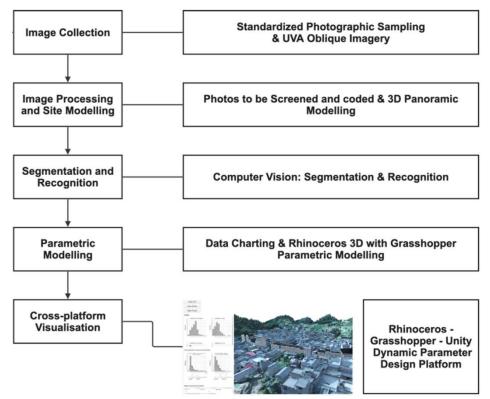

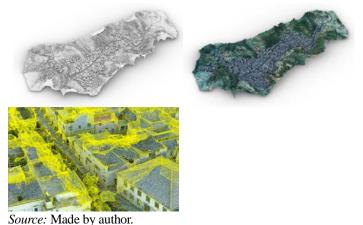

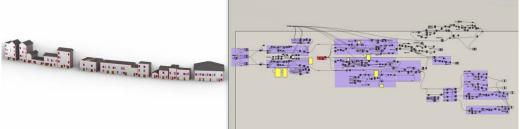

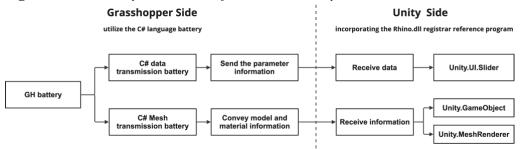

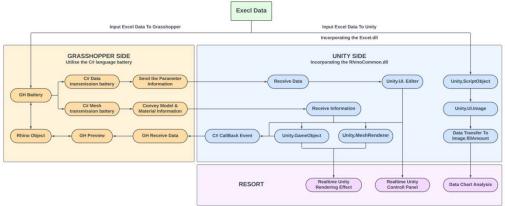

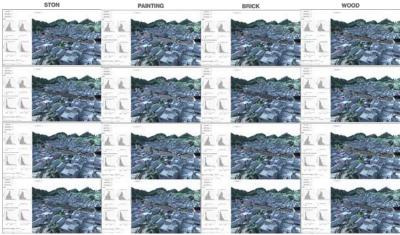

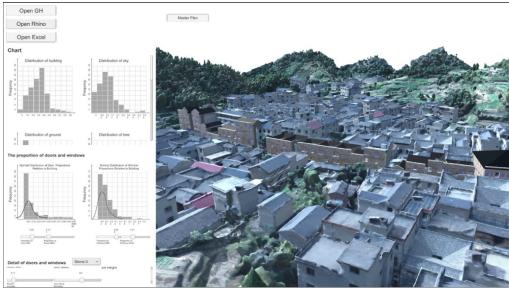

To be Turing-complete, the instructions given with the opcode in Table 1 are implemented. In order to process the instructions, an automaton is generated that was derived from RISC-V and uses the input opcode 6:3 to decode the individual states. In contrast to Harris and Harris (2021), a few states were added because the memory access requires two clock cycles, for example. Consequently, the multicycle processor is divided into the branches load, store, r-type, i-type, b-type, and jal, with the clock cycles split up in order to achieve shorter access times, see Figure 5.